�S����ӹ��I(y��)�İl(f��)չ�������·�ijߴ粻��sС�������ܶȲ������ӣ��S֮�a(ch��n)�����������t����?d��ng)_���������p���ѳɞ��Ƽs��l(f��)չ���P(gu��n)�Iƿ�i���}���@��(du��)�����·��(n��i)���B���x늽��|(zh��)���ϵĽ�늳���(sh��)��k������˸��ߵ�Ҫ��(gu��)�HԪ����ϵ�y(t��ng)���g(sh��)�{(l��n)�Dָ������2028��֮ǰؽ��l(f��)չkֵС��2�ij��ͽ�늳���(sh��)���ϡ��F(xi��n)�еĵ�k���ϣ����������������ЙC(j��)�߷��Ӳ����Լ���ײ��ϵ�ͨ��kֵ����2�Ҵ��ڟ᷀(w��n)���ԡ��C(j��)е�����^��Ȇ��}���y�ԝM�㌍(sh��)�H�ӹ��еĹ�ˇҪ��

�����w�Ѿ۱�������飨POSS�����䃞(y��u)���ğ᷀(w��n)���ԡ����W(xu��)�����Լ���(d��)�صĻ\��Y(ji��)��(g��u)�����J(r��n)�����Ƃ�ͽ�늳���(sh��)�����똋(g��u)����Ԫ�����ϡ�Ȼ������������POSS�ĵ�k���Ͼ����@T8 POSSչ�_����δ���о�̽���\�ӳߴ�����T10��T12 POSS�ڵ�k�����Ƃ��ϵĝ�������Փ������POSS�Ļ\�ӳߴ����������Ŀ�϶���M(j��n)һ�����Ͳ��ϵ�kֵ�����@��Ҫ����?y��n)�T8 POSSͨ���ϳ��Ҵ����̘I(y��)���a(ch��n)Ʒ����T10��T12 POSS���Ƃ估������Ȼ�������^���y�ȡ�

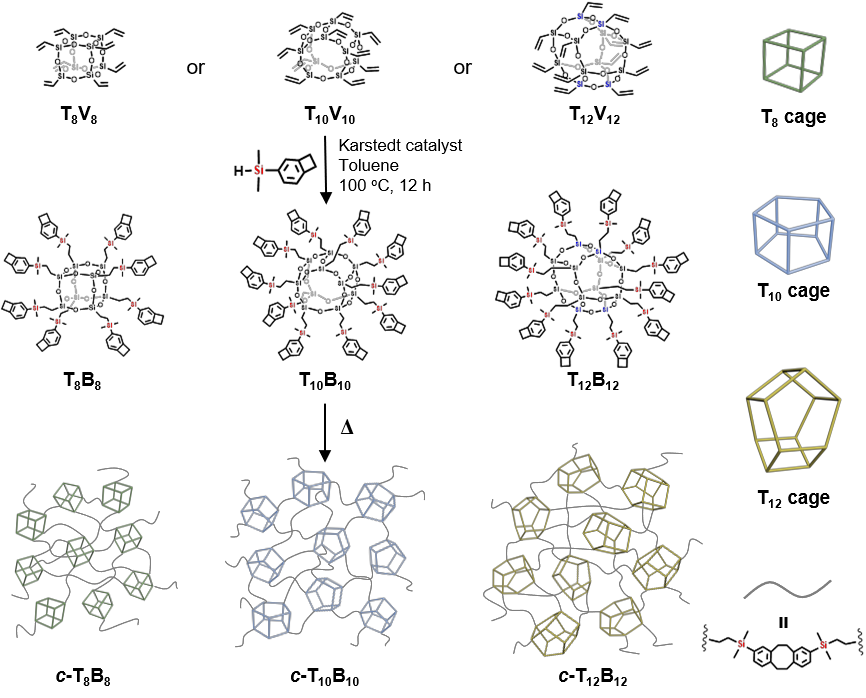

�D1 c-T8B8��c-T10B10��c-T12B12���Ƃ�·���D

�ڱ��о��У������������̘I(y��)������ϩ��POSS������ԭ�ϣ������������������ð���ϩ��POSS��T8V8)��ʮ��ϩ��POSS��T10V10)��ʮ����ϩ��POSS��T12V12���ĘO�Բ���Ό�(sh��)�F(xi��n)�˷��x���S��ͨ�^(gu��)���ӳɷ���(y��ng)�������������˱����h(hu��n)��ϩ���F(tu��n)����(j��ng)�ύ(li��n)�Ƃ�������N�ЙC(j��)-�o(w��)�C(j��)�s�����ϣ�c-T8B8��c-T10B10��c-T12B12�����Ƃ�·����D1��ʾ��

�D2 c-T8B8��c-T10B10��c-T12B12���N��������(y��ng)��POSS�\�w�e�ͽ�늳���(sh��)֮�g���P(gu��n)ϵ�Լ����ڸ���ߴ��T14��T16��T18 POSS�IJ��ϵĽ�늳���(sh��)�A(y��)�y(c��)ֵ

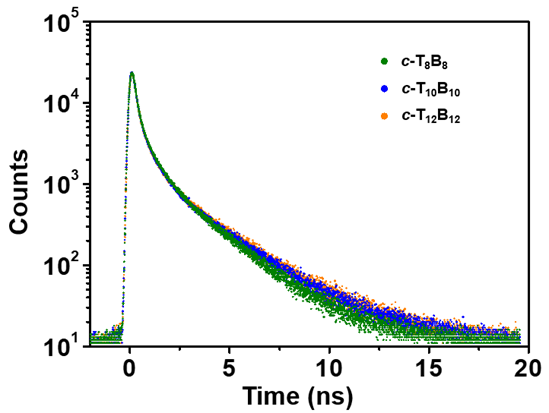

�о��l(f��)�F(xi��n)�S��POSS�\�ӳߴ�����ӣ����ϵ�kֵ�͓p�Ķ��ʬF(xi��n)�½�څ��(sh��)��c-T8B8��c-T10B10��c-T12B12��1 MHz�r(sh��)��kֵ�քe2.24��2.02��1.83���p�ķքe��0.003��0.0018��0.0015����������Μ�����V�C������POSS�\�ӳߴ����x����ϸ���Ŀ�϶���D3�����@Ҳ��kֵ���͵���Ҫԭ����Ȥ���ǣ�ԓ�wϵ�в��ϵ�kֵ�c����(y��ng)POSS���w�e�ʬF(xi��n)�����P(gu��n)ϵ����D2��ʾ���������A(y��)Ҋ���ǣ�ʹ�ø���\�ӳߴ��T14��T16��T18 POSS���������ϵ�kֵ���͵�1.5���¡����⣬���ò���߀�ʬF(xi��n)����(y��u)���ľC�����ܣ�������ԡ��ͱ���ֲڶȣ��D4������(y��u)���ğ᷀(w��n)���Ժ����W(xu��)���ܡ���ˮ�ԣ���ʹ��ˮ�н���3�����300��ߜ��£��@Щ������Ȼ�ܾS�փ�(y��u)���Ľ�����ܣ��D5�������(xi��ng)�������H��C�����܃�(y��u)���ij��ͽ�늳���(sh��)���ϵ��_�l(f��)�ṩ���µ�˼·��Ҳ��δ��(l��i)�����·�ó��ͽ�늳���(sh��)�����ṩ�˂��x��

�D3 c-T8B8��c-T10B10��c-T12B12���N���ϵ�������Μ�����V

�D4 c-T8B8��c-T10B10��c-T12B12���N���ϵ����Ժͱ���ֲڶ�

�D5 c-T8B8��c-T10B10��c-T12B12���N���ϵ� (A) ��ʧ��������(B��25-300��Ľ�늳���(sh��)�͓p�ģ�(C) �ض�-��׃������(D) �{����������(E) ˮ���|�ǣ�(E) ��ˮ�н���3���Ľ�늳���(sh��)�͓p��

���P(gu��n)�ɹ��ԡ�Polyhedral Oligomeric Silsesquioxanes Based Ultralow-k Materials: The Effect of Cage Size���l(f��)����Advanced Functional Materials��Adv. Funct. Mater. 2021, 2102074��DOI��10.1002/adfm.202102074���ϡ�����ͨӍ���ߞ��Ĵ���W(xu��)�߷��ӿƌW(xu��)�c���̌W(xu��)Ժ����(qi��ng)�������n�ϲ�ʿ����һ���ߞ��Ĵ���W(xu��)�߷��ӿƌW(xu��)�c���̌W(xu��)Ժ�Tʿ������������x��(gu��)����Ȼ�ƌW(xu��)������(chu��ng)���о�Ⱥ�w�(xi��ng)Ŀ��No. 51721091���͇�(gu��)����Ȼ�ƌW(xu��)�����������No. 52003173����(du��)�������Ĵ���֧�֣����x�Ĵ���W(xu��)��ϼ������������Μ�����V�y(c��)ԇ�е�֧���c���������x������W(xu��)���ı��о��T�����ʿ�������ļ��g(sh��)֧�ֺ�ӑՓ��Ҳ���x�A��������W(xu��)�h(hu��n)��ͬ�W(xu��)��(du��)���P(gu��n)�Y(ji��)����ӑՓ��

Փ����Ϣ��Adv. Funct. Mater. 2021, 2102074, DOI��10.1002/adfm.202102074

ԭ��朽ӣ�https://onlinelibrary.wiley.com/doi/full/10.1002/adfm.202102074

- �|�A��W(xu��)�TӖ(x��n)�_(d��)�n�}�M ACS Nano������Һ�������wϵ�����c����f(xi��)ͬ�����Ƃ䡰���桱��ۺ����w�� 2025-02-27

- �A��������W(xu��)���S���ڈF(tu��n)�(du��) Macromolecules����������x�o���ij����Ӿۺϼ��g(sh��)�Ƃ����-�ЙC(j��)�����w����Ĥ 2025-01-17

- ���Ĵ�W(xu��)�O�x���ڈF(tu��n)�(du��) Macromolecules�����Ӄ�(n��i)�h(hu��n)���T��(d��o)�ԽM�b�ɿ��Ƃ�����w�{���w�� 2024-12-19

�\(ch��ng)���P(gu��n)ע�߷��ӿƼ�

- ����(b��o)���C(j��)��(hu��)��500+ˎ��...

- ��(gu��)�HƷ�ơ�ǰ�ؕ�(hu��)�h�cչλ�D...

- ������AI�ǿء���Ч�����x��...

- 2025�ؑc����չ���c(di��n)������...

- ��(gu��)�a(ch��n)������٣����(gu��)���^�Ƽ�...

- 2025Ϳ��ԭ���x�ϴ��(hu��)

- �Ј�(ch��ng)��300�|��PMEC China ɫ...

- ����ע��(c��)��2025����������չ...

- ���a���υ��^�A(y��)��ӛ���öY��...

- �ۺ���l(f��)���ИI(y��)���g(sh��)��Ӗ(x��n)����...

- �����ϸ��Լ��ӹ����g(sh��)Ҫ�I(l��ng)��...

- �Ї�(gu��)�ƴ���Ƙ�/���������...

- �B�T��W(xu��)������ڈF(tu��n)�(du��) AFM��...

- �Ľ�ƽ�����A�ƴ�F(tu��n)�(du��)ţȽ��...

- ̫ԭ������W(xu��)�����ֽ��� Adv...

- ����κ�ܽ��ڈF(tu��n)�(du��) CEJ������...

- �Ϸ��Ƽ���W(xu��)�����w���ڈF(tu��n)�(du��)...

- ���ϴ�W(xu��)������/����Ⱥ/����...

- ̫ԭ������W(xu��)�~���/��ʯ��...

- ���_������W(xu��)/�����ش�W(xu��) CR...

- ��h��W(xu��)ꐳ������߶���(l��i)/��...

- ��ƴ��R��l(f��)�݈F(tu��n)�(du��) AFM��...